## Soft Tiles: Capturing Physical Implementation Flexibility for **Tightly-Coupled Parallel Processing Clusters**

Gianna Paulin<sup>1</sup>, Matheus Cavalcante<sup>1</sup>, Paul Scheffler<sup>1</sup>, Luca Bertaccini<sup>1</sup>, Yichao Zhang<sup>1</sup>, Frank Gürkaynak<sup>1</sup>, Luca Benini<sup>1,2</sup> <sup>1</sup>ETH Zurich; <sup>2</sup>University of Bologna

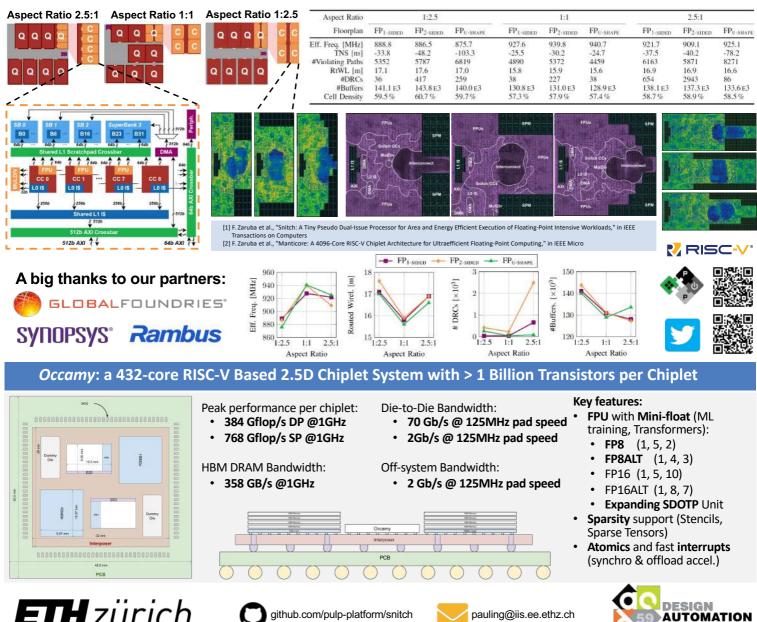

Modern high-performance computing architectures (Multicore, GPU, Manycore) are based on tightly-coupled clusters of processing elements which are physically implemented as rectangular tiles.

Goal: achieve a high utilization for the top-level die floorplan .:

- size and aspect ratio strongly impact the achievable QoR

- as flexible as possible to achieve a high utilization for the top-level die floorplan.

We focus on an open-source, high-performance cluster tile with 8x compute (+1x control) RISC-V cores connected to a shared L1 SPM through a low-latency interconnect [1].

Similar to the state-of-the-art architectures, the cluster tile is then replicated to build a scaled-up high performance acceleration system [2].

We explore the QoR of the physical implementation of this cluster as a soft tile based on a flexible range of aspect ratio and memory macro placement styles for a fixed area of 0.9 mm<sup>2</sup>.

We used Synopsys Fusion Compiler 2020.09 to synthesize, place, and route the cluster in Globalfoundries' 12 nm advanced FinFET technology node at 1 GHz worst-case conditions (SS, 0.72V, 125 °C).

ETH zürich

github.com/pulp-platform/snitch