PULP Features

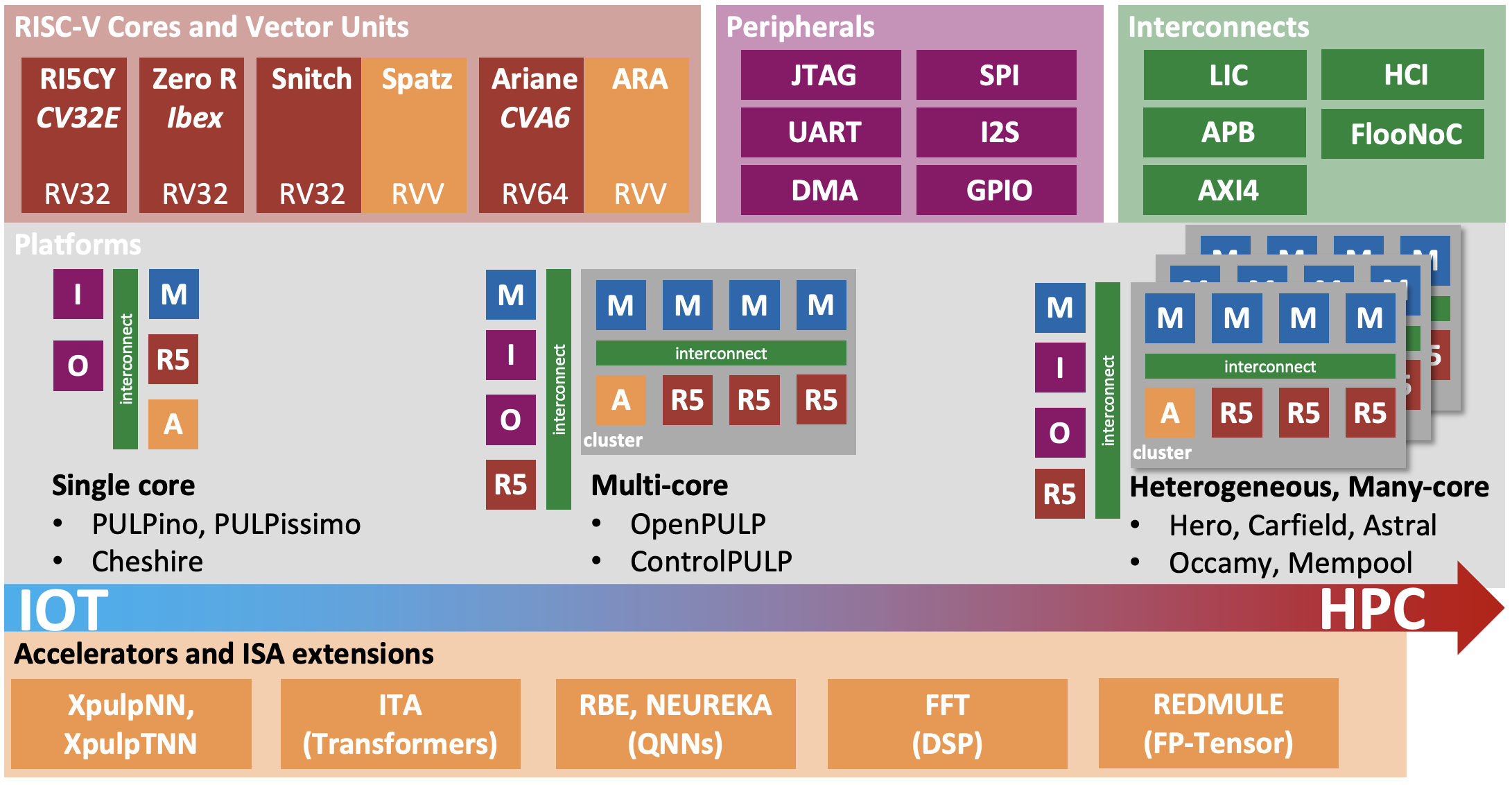

- efficient implementations of RISC-V cores. These include:

- complete systems based on:

- single-core micro-controllers (PULPissimo, PULPino)

- multi-core IoT Processors (OpenPULP)

- multi-cluster heterogeneous accelerators (Hero)

- open-source SolderPad license

- a perpetual, worldwide, non-exclusive, no-charge, royalty-free, irrevocable license

- rich set of peripherals

- I2C, SPI, HyperRAM, GPIO

Do you use PULP?

Does your company or institution use PULP? Please, let us know via email info@pulp-platform.org or send us a direct message on Twitter. We would love to expand our user list.

Meet our mascot

This is our new mascot, Charlie The Bear, the successor of Alex The Bear (until 2019) and Bianca The Bear (until 2023). Just like our previous mascots, Charlie The Bear likes to take pictures with our fans.

Charlie The Bear

Charlie The Bear

Latest news New

12 February 2026

We have coorganized EFCL Winter School with 5 keynotes and 2 parallel tracks. You can find the slides for the talks, lectures ane exercices here.

20 January 2026

We have taped-out Flamingo in 22nm through GF University Partnership Program, combining our open-source Cheshire platform with Spatz vector units and commercial interface IP donated by Synopsys. Read more here.

3 October 2025

Save the dates! We are organizing Winter School on Open Source IC Design and ML acceleration on Feb 9-12, 2026 in Zurich. Find out more here.

27 August 2025

Philippe won The Best Poster award for "34 mm² End-to-End Open-Source 64-bit Linux-Capable RISC-V SoC in 130nm BiCMOS" at Hot Chips 2025. Find his poster here.

31 July 2025

Our paper "A Dynamic Allocation Scheme for Adaptive Shared-memory Mapping on Kilo-core RV Clusters for Attention-based Model Deployment" got the Best Paper Award at ASAP2025 in Vancouver.

Development boards

The following companies sell development boards with chips based on our PULP system:- open-isa.org sells their RV32M1-VEGA development board.

- AI Deck is a collaborative product of GreenWaves, BitCraze and ETH Zurich based on the PULP-shield.

Support

Do you need help with PULP?

We have an Online Forum. Please register and ask your question. Discussions on individual GitHub pages or the following links might be helpful, as well: